AD16 PCB 线路层删除

- 作者: 五速梦信息网

- 时间: 2026年04月04日 13:53

AD16 PCB 线路层删除

- 2024-11-07

一个多月没更新博客园了,这里继续分享关于PCB工程相关一些知识,做过PCB工程都知道用使用genesis或incam是可以非常方便的计算得到铜皮面积这个参数[下图],但实际这个软件是通过什么算法计算出铜面积的呢,这个我们不得而知,但接下来这里介绍一种可以将[线路铜皮面积(残铜率)]计算得出来的方法. 一.计算铜皮面积----公式与参数 1.铜面积公式 公式=[铜面的多边形面积]+[铜的多边形周长*铜厚]-[孔的底面积]+[孔的圆柱面积] 注:看看计算公式是多么简单呀,是吧.下面重点讲[铜面的

1.双面板 在双层板设计layout时,最好不要不成梳状结构,因为这样构成的电路,回路面积较大,但是只要对较重要的信号加以地保护,布线完成之后将空的地方敷上地铜皮,并在多个过孔将两个地连接起来,可以弥补上述的缺点,图3.11的梳状结构的使用于低速电路,PCB信号走向单一,走线密度较低的情况. 图3.11 梳状结构 栅格型地结构,电源和地分别从PCB的顶层和底层,以正交方式引出,在电源和地交叉处放置去耦电容,电容的两端分别接电源和地. 图3.12 栅格结构 2.多层板 有完整地平面的多层板设计的优

好久没画过板了,最近因为工作关系,硬件软件全部得自己来,不得不重新打开闲置很久的AltiumDesigner.以前做过点乱七八糟的笔记,本来想回头翻看一下,结果哪儿也找不到,估计已经被不小心删掉了. 曾经挺熟悉的东西,现在一打开竟然处处遇坎儿,很多操作都忘记了,看来不留好笔记是不行的,不然很多东西过段时间不用,再用的时候就跟新学一样了,还得到处找资料.吸取教训,以后有点什么小note都要有条理的记录收藏起来.PCB各层说明:丝印层(OverLay,Silkscreen):有顶层丝印和底层丝印.用

1.采用的Altium designer 版本为AD16: 2.进入PCB编辑页面,快捷键Ctrl+D,进入视图配置: 3.选择“透明度”,设置选中的层.对象所需的透明度:(横向可以连续选择多个对象,统一设置透明度:纵向只能选中单个对象):

总的来说叠层设计主要要遵从两个规矩: 1. 每个走线层都必须有一个邻近的参考层(电源或地层); 2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容; 下面列出从两层板到八层板的叠层来进行示例讲解: 一.单面PCB板和双面PCB板的叠层 对于两层板来说,由于板层数量少,已经不存在叠层的问题.控制EMI辐射主要从布线和布局来考虑; 单层板和双层板的电磁兼容问题越来越突出.造成这种现象的主要原因就是因信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感.要改善线路的电磁兼容

PCB的各层定义及描述: 1. Top Layer(顶层布线层):设计为顶层铜箔走线.如为单面板则没有该层. 2. Bottom Layer(底层布线层):设计为底层铜箔走线. 3. Top/Bottom Solder(顶层/底层阻焊绿油层):顶层/底层敷设阻焊绿油,以防止铜箔上锡,保持绝缘.在焊盘.过孔及本层非电气走线处阻焊绿油开窗.l 焊盘在设计中默认会开窗(OVERRIDE:0.1016mm),即焊盘露铜箔,外扩0.1016mm,波峰焊时会上锡.建议不做设计变动,以保证可焊性:l 过孔在设

在PCB设计中用得比较多的图层: mechanical 机械层 keepout layer 禁止布线层 Signal layer 信号层 Internal plane layer 内部电源/接地层 top overlay 顶层丝印层 bottom overlay 底层丝印层 top paste 顶层助焊层 bottom paste 底层助焊层 top solder 顶层阻焊层 bottom solder 底层阻焊层 drill guide 过孔引导层 drill drawing 过孔钻孔层 mu

阻焊层:solder mask,是指板子上要上绿油的部分:因为它是负片输出,所以实际上有solder mask的部分实际效果并不上绿油,而是镀锡,呈银白色! 助焊层:paste mask,是机器贴片时要用的,是对应所有贴片元件的焊盘的,大小与toplayer/bottomlayer层一样,是用来开钢网漏锡用的 要点:两个层都是上锡焊接用的,并不是指一个上锡,一个上绿油:那么有没有一个层是指上绿油的层,只要某个区域上有该层,就表示这区域是上绝缘绿油的呢?暂时我还没遇见有这样一个层!我们画的PCB板

1.高版本的AD都没有“Redefine Board Shape” 2.在Keep-Out-Layer层,做好了板子的外形,把外形都选中后,然后快捷键D-S-D即可.

os rm删除的,可以通过os层面恢复(句柄.inode.如果inode没有了可以根据block去重组出来数据文件),也可以通过rman备份还原方式恢复. db 层面drop删除的 只能不完全恢复(基于scn或者timestamp的全库不完全恢复). inode恢复的原理:尽管删除命令只是在文件节点中作删除标记,并不真正清除文件内容,但是其他用户和一些有写盘动作的进程会很快覆盖这些数据. 所以说没有备份的情况下,只要rm后恢复动作只够快,还是能恢复的. 文件从操作系统级别被rm掉,之前打开

Slikscreen_Top :顶层丝印层 Assemly_Top :装配层,就是元器件含铜部分的实际大小,用来产生元器件的装配图.我自己感觉这一层如果对于贴片的元器件,如电容,就是两个贴片铜片的实际大小,而place_bound_top层是 整个贴片元器件的实际大小,这一点很多人都没真正搞懂!也可以使用此层进行布局: Soldermask_Top: 顶层阻焊层 负片输出 Pastemask_Top : 顶层钢板层 加焊层 3.助焊层(Past

一)DXP-设置板层(D+K )在PCB编辑 Design->Layer Stack Manager(层管理) 1)快捷命令 D + K 进入么多层置管理器 2.鼠标右键 TopLayer----> Add signal Layer (创建信号电路层) 此即为创建中间1层, 再鼠标右键 MidLayer1 ---->Add signal Layer(创建信号电路层) 此即为中间1层下面创建了中间2层弄完后

The layers themselves are grouped by their functional types: Signal Layers – Top Layer, Bottom Layer, Mid-Layer 1-30 Internal Planes – Internal Plane 1-16 Other Layers – Drill Guide, Keep-Out Layer, Drill Drawing, Multi-Layer Silkscreen Layers – Top

项目 加工能力 工艺详解 层数 1~6层 层数,是指PCB中的电气层数(敷铜层数).目前嘉立创只接受1~6层板. 板材类型 FR-4板材 板材类型:纸板.半玻纤.全玻纤(FR-4).铝基板,目前嘉立创只接受FR-4板材.如右图 最大尺寸 40cm * 50cm 嘉立创开料裁剪的工作板尺寸为40cm * 50cm,通常允许客户的PCB设计尺寸在38cm * 38cm以内,具体以文件审核为准. 外形尺寸精度 ±0.2mm 板子外形公差±0.2mm. 板厚范围 0.4~2.0mm 嘉立

在设计多层PCB电路板之前,设计者需要首先根据电路的规模.电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板.确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号.这就是多层PCB层叠结构的选择问题.层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段.本节将介绍多层PCB板层叠结构的相关内容.11.1.1 层数的选择和叠加原则确定多层PCB板的层叠结构需要考虑较多的因素.从布线方面来说,层数越

电子元件封装大全及封装常识 电子元件封装大全及封装常识 一.什么叫封装封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳.它不仅起着安装.固定.密封.保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接.因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降.另一方面,封装后的芯片也更便于安

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好.狮屎是不是这样?PCB走线角度该怎样设置,是走45度好还是走圆弧好?90度直角走线到底行不行?这是老wu经常看见广大 PCB Layout 拉线菌热议的话题. 大家开始纠结于pcb走线的拐角角度,也就是近十几二十年的事情.上世纪九十年代初,PC界的霸主Intel主导定制了PCI总线技术(当时的老wu很感谢Intel发布

altium designer 5种走线模式的切换 : shift+space 方格与格点的切换:View-Grids-ToggleVisible Grid Kind源点:Edit-Origin-Set边界的定义:Keep Out Layer-Utility Tools-PlaceLine 按TAB可定义线宽选取元件:PCB-PCB Filter-IS Component逐个放置元件:TOOLS-Component Placement-RepositionSelected Components

一.电路版设计的先期工作 1.利用原理图设计工具绘制原理图,并且生成对应的网络表.当然,有些特殊情况下,如电路版比较简单,已经有了网络表等情况下也可以不进行原理图的设计,直接进入PCB设计系统,在PCB设计系统中,可以直接取用零件封装,人工生成网络表. 2.手工更改网络表将一些元件的固定用脚等原理图上没有的焊盘定义到与它相通的网络上,没任何物理连接的可定义到地或保护地等.将一些原理图和PCB封装库中引脚名称不一致的器件引脚名称改成和PCB封装库中的一致,特别是二.三极管等. 二.画出自己定义的非

一.资料输入阶段1.在流程上接收到的资料是否齐全(包括:原理图.*.brd文件.料单.PCB设计说明以及PCB设计或更改要求.标准化要求说明.工艺设计说明文件)2.确认PCB模板是最新的3. 确认模板的定位器件位置无误4.PCB设计说明以及PCB设计或更改要求.标准化要求说明是否明确5.确认外形图上的禁止布放器件和布线区已在PCB模板上体现6.比较外形图,确认PCB所标注尺寸及公差无误, 金属化孔和非金属化孔定义准确7.确认PCB模板准确无误后最好锁定该结构文件,以免误操作被移动位置二.布局后检

热门专题

相关文章

-

adb sdcard 是否存在

adb sdcard 是否存在

- 互联网

- 2026年04月04日

-

adb查看当前启动App的应用名和包名

adb查看当前启动App的应用名和包名

- 互联网

- 2026年04月04日

-

adb判断设备有没有su

adb判断设备有没有su

- 互联网

- 2026年04月04日

-

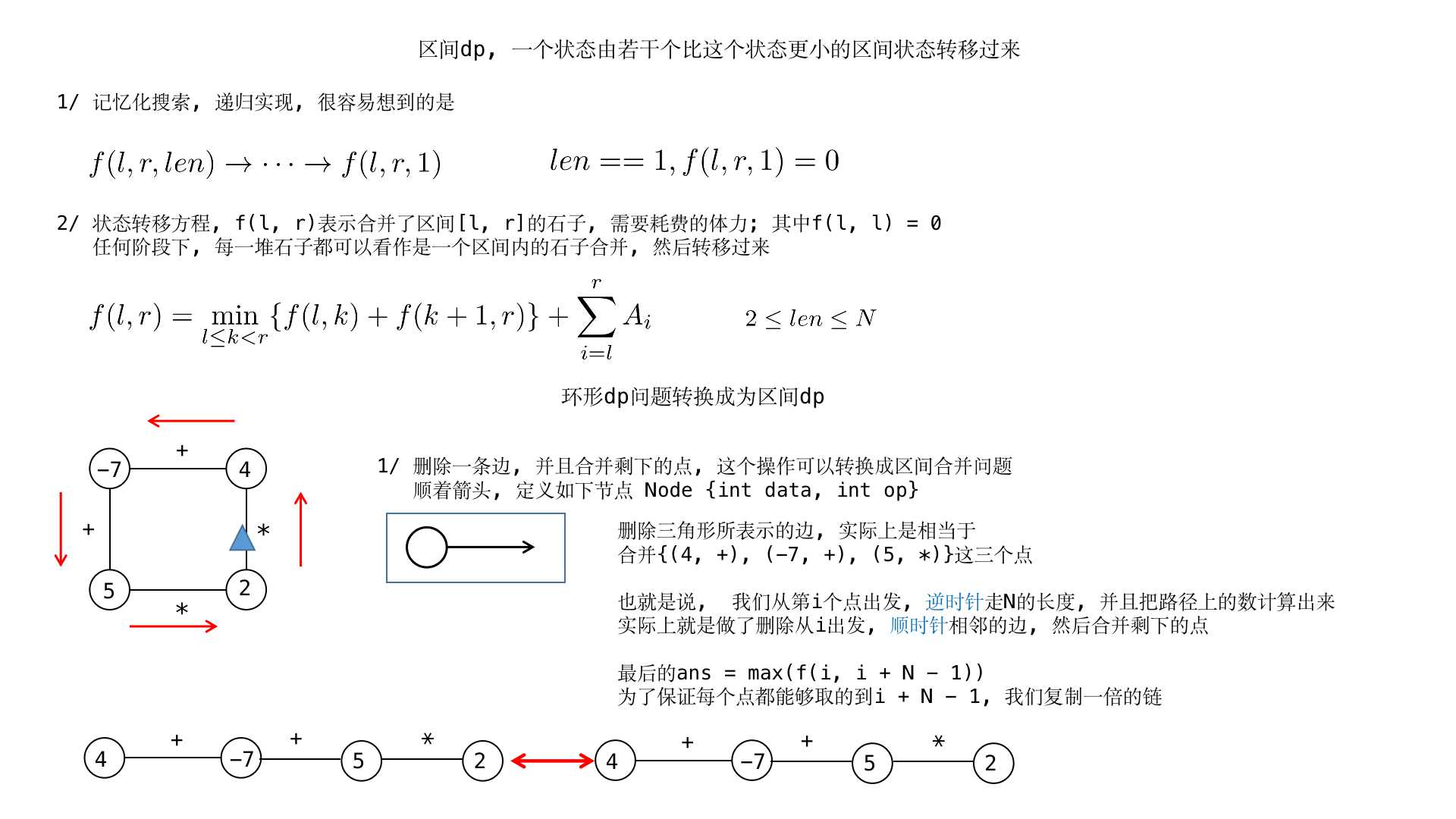

AcWing 284. 金字塔 (区间dp的递归算法和记忆化搜索)

AcWing 284. 金字塔 (区间dp的递归算法和记忆化搜索)

- 互联网

- 2026年04月04日

-

ACwing 196. 质数距离

ACwing 196. 质数距离

- 互联网

- 2026年04月04日

-

activiti中心文档下载

activiti中心文档下载

- 互联网

- 2026年04月04日