arm cortex

- 作者: 五速梦信息网

- 时间: 2026年04月04日 13:50

arm cortex-m3 与DDR

- 2024-10-30

1. keil编译介绍 当使用keil进行单片机的开发时,运行一段程序后,在output输出框会看到如下图的结果. 图1 keil 的output框 其中,Compiler编译器,使用的版本是 V5.06,程序会先经过编译.后链接linking生成可执行的代码,如果要下载单片机的Flash上,还需要转换成二进制(bin)或者十六进制(hex)的文件.具体过程如下: 图2 keil的编译过程 值得注意的是,经过编译后,并不会给变量赋地址(.o文件),只有经过链接器链接后变量才有地址,链接的作用可以

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the project was to use the Serial Wire JTAG protocol implemented in the ARM cortex processors for programming the flash memory of it. JTAG was actually imple

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版本,不过大多的arm7都不带,而大多的arm9的都带.所以一般是arm7跑实时操作系统像ucos做简单的控制应用,而arm9跑linux,cortex是更新一代,分高端的A系列和和低端的M系列,来接arm9和arm7的班 一般情况下ARM7 Cortex-M3 Cortex-M4可以认为是一类,M3

一.Cortex M3的GPIO口特性 在介绍GPIO口功能前,有必要先说明一下M3的结构框图,这样能够更好理解总线结构和GPIO所处的位置. Cortex M3结构框图 从图中可以看出,GPIO口都是接在APB总线上的,而且M3具有两个AHB到APB桥,GPIO则直接接在AHB矩阵上,这样可以减少CPU和DMA控制器之间的竞争冲入,获得较高性能.APB总线桥配置为写缓冲区,使得CPU或DMA控制器可直接操作APB外设,而无需等待总线写操作完成. M3数字I/O功能:高速GPIO口

Cortex-m3启动代码分析笔记 启动代码文件名是STM32F10X.S,它的作用先总结下,然后再分析. 启动代码作用一般是: 1)堆和栈的初始化: 2)中断向量表定义: 3)地址重映射及中断向量表的转移: 4)设置系统时钟频率: 5)中断寄存器的初始化: 6)进入C应用程序. (1)按启动代码的次序,先看堆和栈的初始化: Stack_Size EQU 0x00000200 ;定义Stack_Size为0x00000200 AREA STACK, NOINIT, READWRITE, ALIG

解析 STM32 的启动过程 解析STM32的启动过程 当前的嵌入式应用程序开发过程里,并且C语言成为了绝大部分场合的最佳选择.如此一来main函数似乎成为了理所当然的起点——因为C程序往往从main函数开始执行.但一个经常会被忽略的问题是:微控制器(单片机)上电后,是如何寻找到并执行main函数的呢?很显然微控制器无法从硬件上定位main函数的入口地址,因为使用C语言作为开发语言后,变量/函数的地址便由编译器在编译时自行分配,这样一来main函数的入口地址在微控制器的内部存储空间中不再是绝对不

此书有点深,记录点自己能够看懂的. 1.内存管理一章:讲到变量的类型.生存周期.内存分配. auto static register 局部变量,全局变量 malloc free 内存碎片,消除内存池的一个常见的策略是可以使用分配池 2.共享内存一章:讲到如何编写可重入函数,很多库函数都是设计为可重入函数的,函数体内不能有全局变量和静态变量,有的参数可以通过指针(或二级指针)实现. const类型限定符,使用方法有以下几种: const int p; const int p; int const

ARM架构: 由英国ARM公司设计的一系列32位的RISC微处理器架构总称,现有ARMv1~ARMv8种类. ARM7: 一类采用ARMv3或ARMv4架构的,使用冯诺依曼结构的内核. ARM9: 一类采用ARMv4或ARMv5架构的,使用哈佛结构的内核. Cortex M3: 采用了ARMv7架构的,使用哈佛结构的内核. Cortex M4: 采用了ARMv7架构的,使用哈佛结构的内核.(较前者最大区:别增加了一个DSP处理功能,SIMD单指令多数据功能.其他区别请自

STM32学习之路入门篇之指令集及cortex——m3的存储系统 一.汇编语言基础 一).汇编语言:基本语法 1.汇编指令最典型的书写模式: 标号 操作码 操作数1, 操作数2,... :注释 1).标号是可选的,如果有,它必须顶格写.标号的作用是让汇编器来计算程序转移的地址. 2).操作码是指令的助记符,它的前面必须有至少一个空白符,通常使用提个Tab键来产生. 3).操作码后面往往跟若干个操作数,而第一个操作数,通常都给出本指令执行结果的存储地.不同指令需要不同数目的操作数,并

Introducing swddude I love the ARM Cortex-M series of microcontrollers. The sheer computational power they pack into a teensy, low-power package is almost embarrassing. But, many Cortex-M parts are small — 4x4 millimeters small — and don’t have the

灵动微电子ARM Cortex M0 MM32F0010 GPIO的配置 目录: 1.前言 2.学习方法简要说明 3.要点提示 4.注意事项 5.MM32F0010系统时钟的配置 6.MM32F0010的GPIO初始化配置 7.MM32F0010 GPIOA PA7驱动LED灯每隔一秒翻转一次 1.前言: MM32F0010是基于ARM Cortex M0核的32位微控制器(MCU)即32位的单片机,使用库函数开发,每一个片上外设都有与之对应的外设xx.c和xx.h库函数,例如:hal_rcc.

目录 前言 posix 标准接口层设计 模拟器的系统心跳 模拟器的task底层实质 模拟器的任务切换原理 cortex M3/M4异常处理 双堆栈指针 双操作模式 栈帧 EXC_RETURN 前言 如果对硬件任务内核切换不感兴趣的同学可以跳过. 由于任务源码分析开始涉及到接口层,所以在学习源码前,先了解下posix接口层的设计. 本系列接口层会讲解两个: posix标准接口.因为本教程demo在linux上跑freertos时实际使用的就是这个接口. cortex m3/m4架构接口.因为这才是

灵动微电子ARM Cortex M0 MM32F0010 UART1和UART2中断接收数据 目录: 1.MM32F0010UART简介 2.MM32F0010UART特性 3.MM32F0010使用UART2的注意事项 4.MM32F0010UART中断接收的初始化配置 5.MM32F0010UART中断接收函数的编写 6.MM32F0010UART查询方式发送数据函数的编写 7.MM32F0010UART处理接收数据函数的编写 1.MM32F0010UART简介: MM32F0010的通用异

灵动微电子ARM Cortex M0 MM32F0010 Timer定时器中断定时功能的配置 目录: 1.Timer1高级定时器Timer3通用定时器Timer14基本定时器简介 2.Timer1高级定时器Timer3通用定时器Timer14基本定时器功能特性 3.Timer1高级定时器Timer3通用定时器Timer14基本定时器实现基本定时中断功能的初始化配置 4.Timer1高级定时器Timer3通用定时器Timer14基本定时器实现基本定时中断功能,分别定时1ms/5ms/1s并分别翻转

JTAG was the traditional mechanism for debug connections for ARM7/9 parts, but with the Cortex-M family, ARM introduced the Serial Wire Debug (SWD) Interface. SWD is designed to reduce the pin count required for debug from the 5 used by JTAG (includi

1.stm32综述 2.寄存器组 3.操作模式和特权级别 4.存储器映射 5.中断和异常 6.其他 Stm32综述 这可以说是我第一款认真学习的单片机了,学完这个就要开启我通往arm9的大门了,接下来把我学到的东西做一个系统的概述: 上图是stm32的系统结构. 使用哈弗体系结构,取指和取数据分离, ICODE指令总线连接到flash闪存指令存储区,这个存储区的地址在0x00000000-0x1FFFFFFF之间,负责取指操作. DCODE数据总线负责在0x00000000-0x1FFFFFFF

i.MX6UL: i.MX 6UltraLite处理器 - 低功耗,安全,Arm Cortex-A7内核 概述 MX6UltraLite作为i.MX6系列的扩展,一系列高性能.超高效的处理器,采用先进的Arm Cortex-A7内核,运行速度高达696 MHz.i.MX6UltraLite应用处理器包括一个集成的电源管理模块,降低了外接电源的复杂性,并简化了上电时序.这个系列的每个处理器提供多种存储器接口,其中包括16位LPDDR2.DDR3.DDR3L.原始和管理的NAND闪存.NOR闪存.e

http://www.zembedded.com/cortex-m3-registers-in-depth/ Thanks for the overwhelm response you show in our first tutorial on Cortex_M3 series controllers. This is going to be the second tutorial, where we are going to discuss about the registers availa

http://infocenter.arm.com/help/advanced/help.jsp 在这里输入合适的版号即可 这样就可以不用去 CSDN 了 100000_0000_00_EN - ARM CoreLink DMC-520 Dynamic Memory Controller Technical Reference Manual100000_0001_00_EN - ARM CoreLink DMC-520 Dynamic Memory Controller Technical Re

热门专题

- 上一篇: armv8 neon vget

- 下一篇: arduino 字符解析

相关文章

-

armv8 neon vget

armv8 neon vget

- 互联网

- 2026年04月04日

-

ascx aspx ashx asmx 文件的作用

ascx aspx ashx asmx 文件的作用

- 互联网

- 2026年04月04日

-

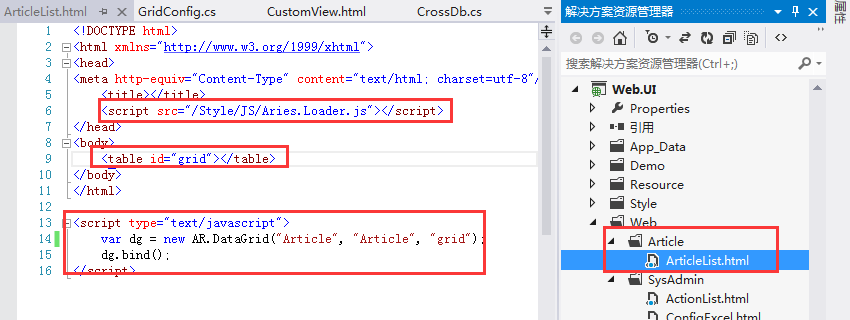

ASP.NET Aries 入门开发教程3:开发一个列表页面及操控查询区

ASP.NET Aries 入门开发教程3:开发一个列表页面及操控查询区

- 互联网

- 2026年04月04日

-

arduino 字符解析

arduino 字符解析

- 互联网

- 2026年04月04日

-

arduino 计数器中断

arduino 计数器中断

- 互联网

- 2026年04月04日

-

arcmap vba 数字转换字符串

arcmap vba 数字转换字符串

- 互联网

- 2026年04月04日